-

Amira Abdel-Rahman authoredAmira Abdel-Rahman authored

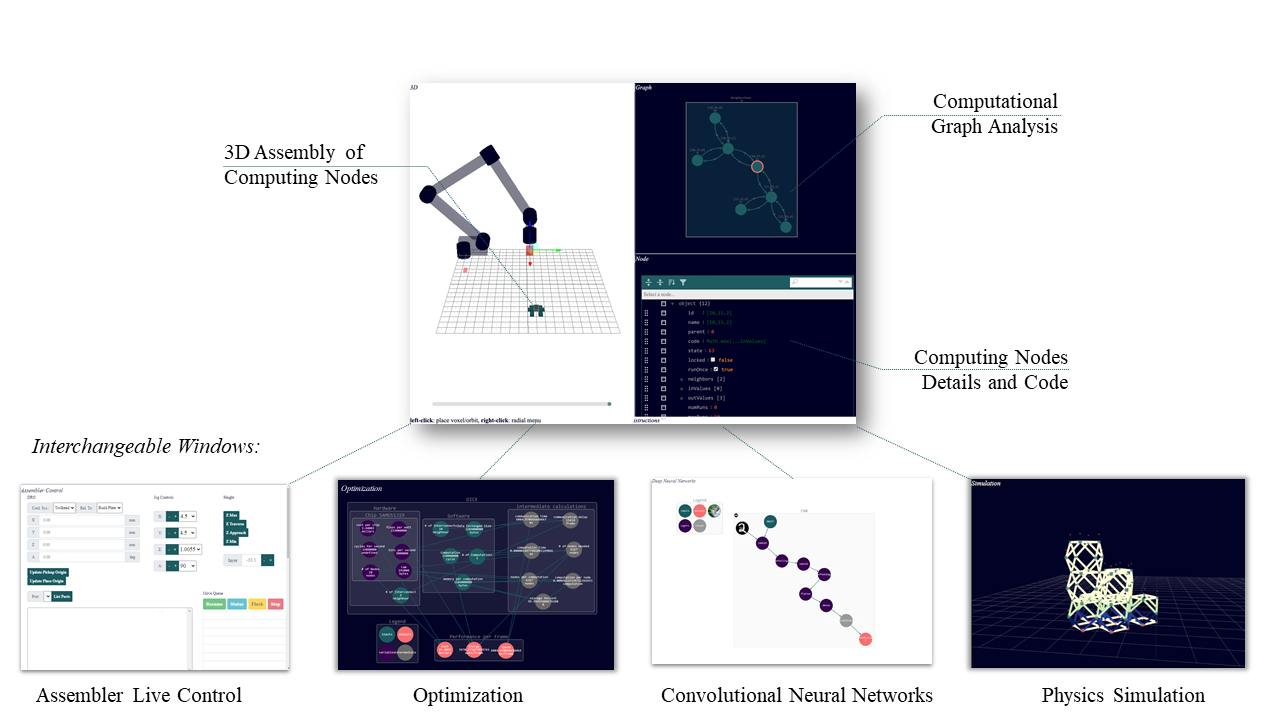

Physical Computing Design Tools (PC Tools)

Description

The Physical Computing Design tool is an integrated design tool for the design, simulation, optimization and fabrication of reconfigurable computing systems.

Traditional electronics design workflows follow a sequential linear process that starts with design, then analysis and simulation, and finally system fabrication and testing. Often these stages are executed independently from each other, using different tools, making it hard to translate the feedback from the simulation or testing stages into viable design amendments. This adds considerable inefficiency to an inherently iterative design workflow. As an alternative, we developed an integrated, closed loop DICE design tool where one can design, simulate, optimize and fabricate re-configurable computing systems

The following steps explain in detail the proposed design workflow:

- Design: The first step is to place the DICE nodes and visualize the 3D assembly of the computing system.

- Programming: The user then selects individual nodes to specify details, such as processor type, connected neighbors, program, number of operations, maximum token size, and so forth. During these steps, a connectivity graph is generated in real-time, showing the average computation and communication cost of each node based on these preprogrammed node details. In the future, these numbers could be automatically calculated by pre-compiling and profiling code for each node.

- Analysis: By treating the computation graph as a flow network, graphical algorithms are used to find and highlight computation and communication bottlenecks. Based on this analysis, design recommendations are generated and displayed, including suggestions for different processors, extra nodes, or alternative routing.

- Optimization: If the user wants to further optimize the reconfigurable computing system, the performance projection graph tool visualizes the effect of each hardware and software decision on projected overall system performance. A generative probabilistic programming model is used to draw samples from these inputs and project the cost, energy use, and speed of the system. Using classic inference techniques one is able to infer the optimal hardware configuration for a given software workflow. In the future this could be extended to additionally perform hardware architecture discovery.

- Simulation: the simulation window allows the user to visualize the state and output of the DICE computation. Currently, this shows the output of a simulated computation provided on the host computer prior to physical assembly. In the future, this framework will be used to visualize data from the DICE network.

- Fabrication: In parallel with the previous steps, the real-time assembly control window provides a simple mechanism for controlling the mechanical DICE assembler. Using this feature, systems can be fabricated, programmed, and tested in real-time to quickly pull in feedback and amend the system architecture accordingly.

This novel integrated design workflow paves the way for the design of discrete integrated circuits but also reconfigurable computing systems that can change and evolve while execution as needed.

Progress

Demo Links

- "Physical Computing Interface"

- "Performance Calculation Graph" demo lives here.

- Distributed Deep Neural Networks

- UR10 voxel Assembly demo.