-

Amira Abdel-Rahman authoredAmira Abdel-Rahman authored

Physical Computing Design Tools

Description

The Physical Computing Design tool is an integrated design tool for the design, simulation, optimization and fabrication of reconfigurable computing systems.

Traditional electronics design workflows follow a three stage sequential linear process that starts with the design of the system, then the analysis and simulation, and finally the fabrication and testing of these systems. Very often these stages are executed independently from each other, using different tools and sometimes different teams, making it very hard to translate the feedback from the simulation or testing stages into viable design amendments. This results in the design workflow, which is an inherently iterative process, being be a very tedious and inefficient process.

Therefore, we present an integrated, closed loop physical computing design tool where one can design, simulate, optimize and fabricate reconfigurable computing systems.

The following steps explain in detail the proposed design workflow:

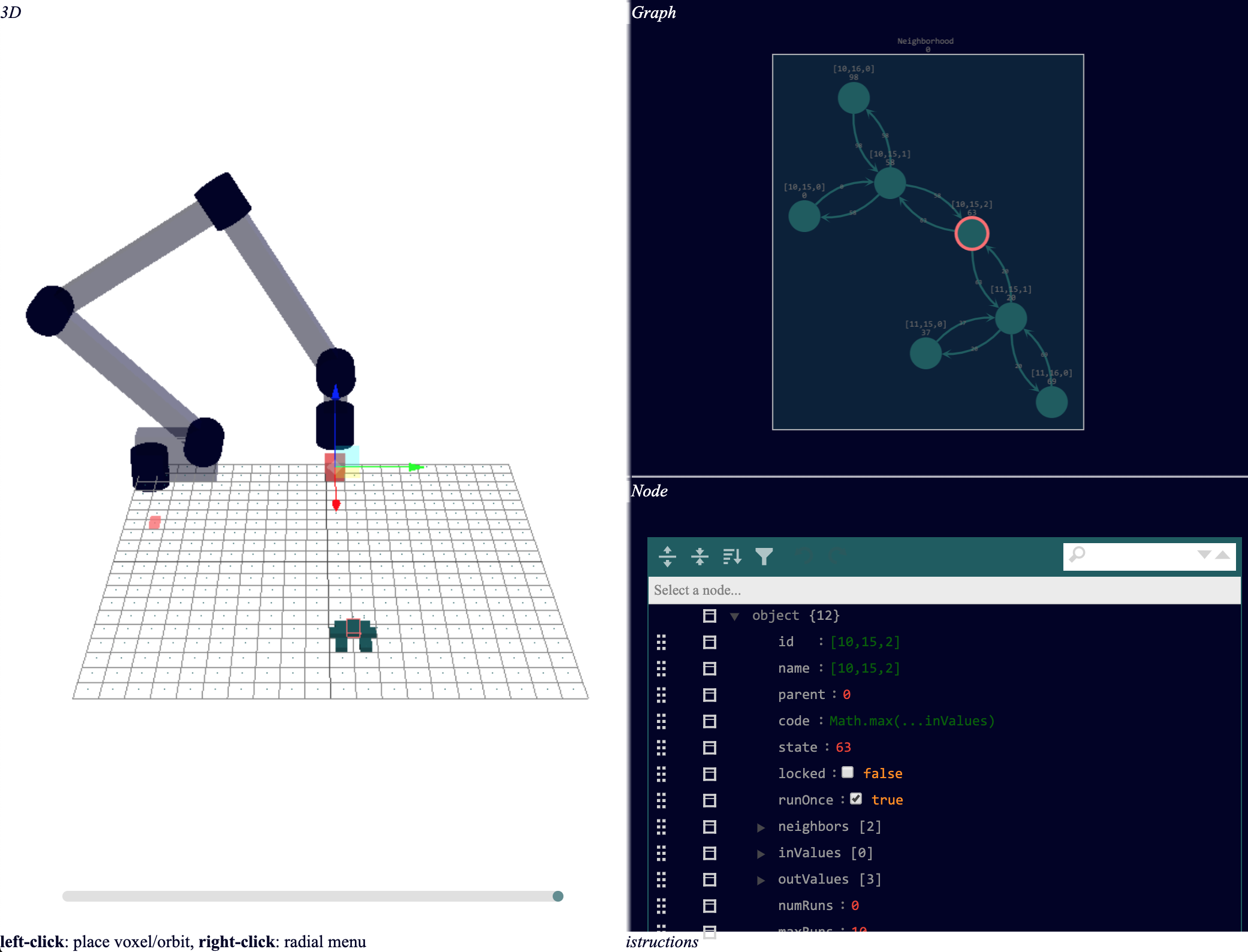

- Design: The first step is to place the DICE nodes and visualize the 3D assembly of the computing system.

- Programming: Next, one should select each node and specify the node details (code/program, processor, connected neighbors, starting state.. etc).

- Analysis: While placing multiple parts (an assembly), an analysis of the whole computation graph is automatically generated in realtime (average computation per frame, communication bottlenecks, connectivity graph, hierarchal graph), and custom code for application specific analysis could be added. Based this analysis, design recommendation are generated and displayed. For example, using another type of processor, adding extra nodes to divide the computation of overloaded nodes into two, finding more efficient routing for data transfer.

- Optimization: If one wants to further optimize the reconfigurable computing system, the performance projection graph tool visualizes how each hardware and software decision/variable is affecting the projected performance (energy use, speed, cost). There, one describes each input variable as a distribution (normal, categorical..) and a probabilistic programming model is used to infer what is the optimal hardware configuration for the given software workflow.

- Simulation: The simulation window has a visualization of the state and output of the DICE computation. This is either the output of the simulation of DICE computation on the computer before assembling and building the system or later visualizing the data sent back from the DICE system.

- Fabrication: In parallel to the previous steps, the assembly realtime control window makes it very easily to control the assembler and fabricate, program, test the designed systems in realtime and to get feedback and amend the system accordingly.

This novel integrated design workflow paves the way for the design of discrete integrated circuits but also reconfigurable computing systems that can change and evolve while execution as needed.

Progress

Demo Links

- "Physical Computing Interface"

- "Performance Calculation Graph" demo lives here.

- Distributed Deep Neural Networks

- UR10 voxel Assembly demo.

Demo Videos

Capabilities and Updates

- Design

- Parametric grid definition (cubic, hexagonal, dice)

- Assembly/timeline

- Timeline for future morphing computing

- UR10

- Graph

- Hierarchy

- Automatic neighborhood

- highlights

- Computing

- Asynchronous code propagation (distributed max example)

- Simple test case find max value distributed

- Min cut max flow concept study neighborhood

- Hardware optimization

- see section below.

- Improved UI and integration

- Radial menu

- Json propagation

- Highlight selected node

- switch windows

- Applications

- voxel design tools

- Convolutional neural networks

Applications

- The most efficient applications for dice are those who need reconfiguration white running, examples:

- probabilistic programming (Gamalon)

- more computing power while assembling voxels

- Neural Networks?